Verilog Code For Serial Adder Circuit

Contents • • • • • • • • • • • • • • • Full-Adder in Verilog Review A full adder is a combinational logic that takes 3 bits, a, b, and carry-in, and outputs their sum, in the form of two bits, carry-out, and sum. The figure below illustrates the circuit: New Project • The first task is start the Xilinx ISE and create a New Project. Let's call it FourBitAdder. • Once the Project is created, add a New Source, of type Verilog Module. Call it SingleStage.

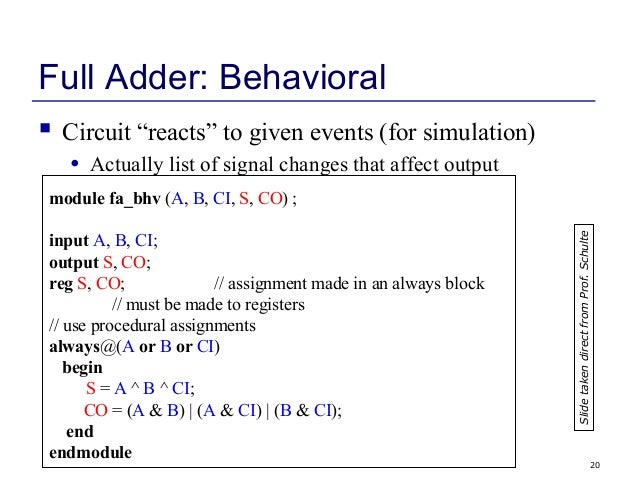

It will contain the full-adder for 2 bits. • Define the ports as follows: • a, input • b, input • cin, input • s, output • cout, output We now have several options to define this adder. One is functional, as illustrated in the next subsection. Next is a logical description, where we express the outputs in terms of their logical equation. The final is a gate level description. Pick the one that seem most interesting to you.

They should all yield the same result in the next section, where we test them. Functional Description of Full Adder. Module MultiStages ( input [ 3: 0 ] a, input [ 3: 0 ] b, output [ 3: 0 ] sum, output carry ); wire cin; assign cin = 1 'b0; SingleStage s0 (. A ( a [ 0 ] ),. B ( b [ 0 ]),.

Cin ( cin ),. S ( sum [ 0 ]),. Cout ( ripple0 ) ); SingleStage s1 (. George Foreman Grill Cooking Times Bratwurst Seasoning. A ( a [ 1 ] ),. B ( b [ 1 ]),.

Cin ( ripple0 ),. S ( sum [ 1 ]),. Cout ( ripple1 ) ); SingleStage s2 (. A ( a [ 2 ] ),. B ( b [ 2 ]),. Cin ( ripple1 ),. S ( sum [ 2 ]),. Demonoid Photoshop Cs5 Keygen.